# Video Processing and Retrieval on Cell Processor Architecture

Junqing Yu, Haitao Wei

Computer College of Science & Technology, Huazhong University of Science & Technology, Wuhan, 430074, China yjqing@hust.edu.cn, whtaohust@163.com

Abstract. A multi-level parallel partition schema and three mapping model – Service, Streaming and OpenMP model – are proposed to map video processing and retrieval (VPR) workloads to Cell processor. We present a task and data parallel partition scheme to partition and distribute intensive computation workloads of VPR to exploit the parallelism of a sequential program through the different processing core on Cell. To facilitate the VPR programming on Cell, OpenMP programming model is loaded to Cell. Some effective mapping strategies are also presented to conduct the thread creating and data handling between the different processors and reduce the overhead of system performance. The experimental results show that such parallel partition schema and mapping model can be effective to speed up VPR processing on Cell multicore architecture.

# 1 Introduction

Nowadays, with the rapid development of multimedia and network technologies, digital video information has grown exponentially. Digital video rapidly becomes an important source for information, education and entertainment. It is much easier to access video content via network than ever. How to help people conveniently and fast retrieve the interested video content is becoming more and more important. To this aim, content-based video processing and retrieval (VPR) is extremely needed. VPR has been an international research focus in multimedia domain. However, the intrinsic features of video, such as rich and non-structured data, intensive computing, and complex algorism, have prohibited VPR's further development. VPR programming is challenging and real-time processing and parallelization are expected.

Multi-core chip architecture is becoming the mainstream solution for next generation microprocessor chips. Cell processor, developed by IBM/Sony/Toshiba, provides an efficient high performance computation platform, with 9 cores one PowerPC Processor Element (PPE) and eight Synergistic Processor Elements (SPE). In order to meet the intensive computation and the real-time processing, we port VPR to Cell multi-core processor, with each core performs a part of VPR processing. A multi-level parallel partition schema and three mapping model (Service, Streaming and OpenMP model) are proposed to map VPR workload to the 9 cores of Cell.

## 2 Junqing Yu, Haitao Wei

The rest of this paper is organized as follows. In section 2, we try to use Service and Streaming model to map VPR workloads to Cell. It is proposed to map OpenMP programming model to Cell in section 3. Section 4 concludes this paper.

# 2 Video Processing and Retrieval on Cell

As digital video data becomes more pervasive, mining information from video data becomes increasingly important, but the huge computation prohibits its wide use in practice. Accelerating the video processing application by exploiting multi-level parallelism on Cell would be a promising way to boost the performance and provide more functionality for VPR.

#### 2.1 Cell Architecture Overview

The first-generation Cell processor consists of a 64-bit multithreaded Power PowerPC processor element (PPE) and eight synergistic processor elements (SPE) connected by an internal, high-bandwidths Element Interconnect Bus (EIB) [1]. The PPE contains two levels of globally coherent cache and also supports Vector/SIMD Multimedia Extension (VMX) instruction set to accelerate multimedia and vector application [2]. The major powerful computation ability derives from the eight SPEs. Each SPE contains non-coherent local store for instructions and data.

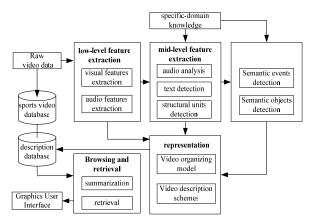

Fig. 1. Overview of video processing and retrieval framework

## 2.2 Video Processing and Retrieval Framework

Video processing and retrieval aims to help users to search, browse and manage video contents easily. The key components include low-level feature extraction such as visual and audio features, shot boundary detection, scene segmentation, video structural summary, high level semantic concept detection, annotation, indexing and

content-based video retrieval [3]. We propose an efficient framework for indexing, browsing, abstracting and retrieval of sports video. As illustrated in Fig. 1, the framework consists of five stages: low-level feature extraction, mid-level feature extraction, high-level feature extraction, proving and retrieval as well. In these five stages, there exist multi-level parallelisms, such as feature extraction, indexing and retrieval, which can be exploited intensively.

## 2.3 Service and Streaming Programming Model for VPR on Cell

The key characteristics of VPR application are variety of tasks and intensity of computation. Therefore, the Service Model and the Streaming Model are proposed to be the best candidates.

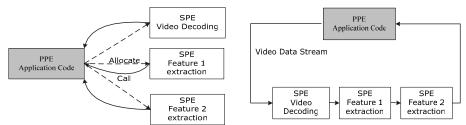

Fig. 2. Service Model of Video Processing

Fig. 3. Stream Model of Video Processing

Fig. 2 shows the Service Model in video processing. The processor assigns different services to different coprocessors, and the processor's main process calls upon the appropriate coprocessor when a particular service is needed. It is well known that feature extraction is a basic and important step in video processing. Here, each feature extraction is regarded as a service, which is assigned to one or more coprocessors and the processor's main process call upon these coprocessors' services needed. Fixed static allocation of coprocessors' services is avoided. These services are virtualized and managed on a demand-initiated basis.

Fig. 3 illustrates the Streaming Model, the main processor acts as a stream controller, and the coprocessors act as stream-data processors in either a serial or parallel pipeline. In video processing, each procedure has inherent computing stage which is mapped to one coprocessor. Here, the first coprocessor decodes the input raw video data stream and outputs decoded video data stream. The second coprocessor takes the decoded video data stream as input and extracts the feature 1 in stage 2. Finally, the third coprocessor extracts feature 2 and output the result data to the main processor. Under the control of the main processor, all the coprocessors work together in a pipeline to speed up the computation performance.

# 2.4 Block Matching Algorithm on Cell Using Parallel Partition

## 2.4.1 Block Matching Algorithm

Block matching algorithm is an important step of motion compensation algorithms for inter-frame predictive coding, which is used to eliminate the large amount of temporal

and spatial redundancy that exists in video sequences and helps in compressing them. These algorithms estimate the amount of motion on a block by block basis, i.e. for each block in the current frame i, a block from the previous/after frame j is found, that is said to match this block based on a certain criterion.

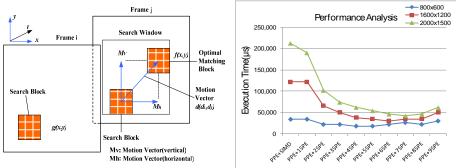

Here, the block matching criteria is the sum of absolute differences and the algorithm is Full Search or the Exhaustive Search. As Fig.4 shown, each block within a given search window in frame j is compared to the current search block g(x,y) in frame i. At each search step, the sum of absolute differences between the search block and the given block f(x,y) is evaluated using the following criterion.

$$AE = \sum_{i=1}^{K} \sum_{j=1}^{K} \left| f(i, j) - g(i - d_x, j - d_y) \right|$$

(1)

Where, K means the size of the block,  $d_x$  and  $d_y$  refers to the motion vector, which means amount of motion from the current block to the aim block. The best match is obtained if AE achieves the minimum.

Fig.4. Illustration of Block Matching

Fig. 5. Performance Analysis on Block Matching

## 2.4.2 Parallel Scheme of Block Matching Algorithm

The sequential algorithm uses four nested loops to evaluate the minimum AE. As the program following, array Block[8][8] and Frame[M][N] are allocated for the current search block and search window respectively, and variable diff preserves the absolute difference at each searching step. The minimum absolute difference and corresponding motion vector are stored in variable min, x and y respectively.

```

For(i=0;i<M-7;i++)

for(j=0;j<N-7;j++){

for(l=0;k<8;l++)

for(m=0;l<8;m++)

diff+=abs(Block[k][l]- Frame[k+i][l+j]);

if(diff<min)

{min=diff;x=i;y=j;}

}</pre>

```

In order to contrast the performance improvement and communication overhead generated by different level parallelism, a step by step parallel scheme is adopted on Cell. In the first step, we SIMDize the code for PPE to attain the data level parallelism, and then port the PPE code to multiple SPEs to achieve the task and data level parallelism. Finally, the overhead of communication is measured by setting the number of thread to one.

#### Scheme 1: SIMDize the code for execution on PPE

The main idea in this scheme is to utilize the VMX instruction set to accelerate the data computation. VMX instructions-vec\_perm, vec\_abs, vec\_add, and vec\_sumsare used to execute the vector absolute evaluation by allocating the array block[8][8] and frame[M][N] into one dimension array of vector. By this way, computation complexity is reduced by about 8 times and the number of loops is decreased to 3.

#### Scheme 2: Parallelize Code for Execution across Multiple SPEs

PPE initializes to partition and distribute the task to each SPE. It divided the search window into some sub-windows, and then maps the matching procedure in each sub-window to each SPE to evaluate the local minimum of AE and correlative local motion vector. In the end, PPE reduces the global AE and correlative global motion vector comparing all the local AE. SPEs receive the sub-window and current block from PPE, search the best local match to get the local minimum of AE and correlative motion vector, and sends the results to PPE to evaluate the global AE and motion vector.

The different instruction set between PPE and SPE makes the program running on Cell partitioned into two sections – PPE code for PPE and SPE code for SPE. The following *PPE Code* shows that the subroutine *spe\_create\_thread* creates a group threads running on SPE, the address of the data can be transmitted through the parameter ctx. After the threads are created, subroutine *spe\_wait* is called to wait all the SPE threads to finish. At last, PPE gets the global result from local result returned from the SPE. In the *SPE Code*, each SPE gains the data from PPE through DMA transform, and then evaluates local minimum *AE* and the coordinate motion vector with SIMD instruction in SPE. After matching, each SPE sends the result to PPE by DMA.

## PPE Code:

```

//correspond to 'fork' in OpenMP

For(i=0,offset=0;i<SPE_THREADS;i++,offset+=P){

// Create SPE thread of execution passing the context

as a parameter.

spe_ids[i] = spe_create_thread(0, &match_multi_spu,

&ctx[i], NULL, -1, 0); }

...

// correspond to 'join' in OpenMP

for(i=0;i<SPE_THREADS;i++){

(void)spe_wait(spe_ids[i],&status,0); }

//find the globe minimum, coordinate x,y

for (i=0; i<SPE_THREADS;i++){

if(diff[i]<globemin)</pre>

```

```

{globemin=diff[i];x=posx[i];y=posy[i];}

}

SPE Code:

...

//gain the data from ppe

spu_mfcdma32(..., MFC_GET_CMD);

...

//compute the absolute and the local minimum and

//the coordinate x,y with SIMD instruction in spu.

...

uschRowAbs_v[k]=spu_absd(model_v[k],uschRow_v[k]);

if(diff[k]<localmin)

{localmin=diff[i];x=posx[k];y=posy[k];}

...

spu_mfcdma32(..., MFC_PET_CMD); //return the resulte</pre>

```

#### Scheme 3: Set 1 thread to Measure the Communication Overhead

Comparing to the program only running on PPE without communication with SPE, the program is ported to one SPE to measure the communication overhead setting the MARO SPE\_THREADS of the SPE thread to one.

#### 2.4.3 Experimental Results

The experiment of block matching algorithm was realized on IBM Cell simulator v2.0, using the language of PPE SPE C/C++ language extension (Intrinsics), with the SDK v2.0 [4]. As Fig. 5 shows, parallelization boosts the performance dramatically with the resolution accreting. Here, approximate 5x speedup is achieved referring to the resolution of  $2000\times1500$  contrasting to 2x speedup referring to resolution of  $800\times600$ . The performance achieves a peak with SPE increasing, but over parallelization deteriorates the performance. Referring to the resolution of  $800\times600$ ,  $1600\times1200$ , and  $2000\times1500$ , the number of SPE to achieve the best performance is 4, 6, 7, respectively. It is illustrated that with the SPE increasing, the computation ability is strengthened, but the communication overhead is expanding as well. Only when the balance point reaches, the best performance is achieved.

# 3 Loading OpenMP Programming to Cell

Cell provides an efficient computation resource for application of intensive computation with the data and the task level parallelism. But, programming on Cell for VPR is not an easy job, e.g., the block matching algorithm in section 3, programmer has to be acquainted with the Cell architecture, PPE and SPE instruction sets, DMA transfer, and register files, etc. Although suit for VPR, Service and Streaming models are low level and inconvenient. All of these constrain the improvement of facility and performance for programming. OpenMP is an industrial standard for shared memory parallel programming agreed on by a consortium of

software and hardware vendors [5]. It consists of a collection of compiler directives, library routines, and environment variables that can be easily used for VPR programming on Cell [6].

#### 3.1 Loading Strategy

The parallel computation needs to be split among PPE and SPE processors. The parallelism is represented in OpenMP using "parallel" directive. PPE and SPE processors can be viewed as a group of "threads". Through data allocation PPE tells each SPE processor to execute specific regions in parallel. PPE executes the region as the master thread of the team. At the end of a parallel region, PPE waits for all other SPE to finish and collect the required data from each SPE [7, 8].

## 3.2 Exploitation Locality

The shared data is allocated in the main storage of PPE, and can be accessed exclusively through the atomic operation on Cell. Operation on shared data, each SPE needs to translate the local address to the effective address. The solution is to keep a copy of the shared data in the local storage of each SPE instead of the direct accessing to main storage when reading/writing the shared data. Then, if the local copy of the shared data is updated, the changed data will be written through DMA transfers back to the main storage after the end of parallel section.

## 3.3 Parallel Synchronization

The parallel synchronization is implemented with the mechanisms of memory tag polling and event trigger on Cell. The first method is to allocate a tag memory for each SPE with values initialized to "0" and each SPE polls the tag to wait the task assigned by PPE. PPE wakes up each SPE by setting the tag to "1". If detecting the tag set to "1", then each SPE runs the computation immediately, and after the computation is completed, the tag is set to "2" to notice PPE. At the same time, the PPE polls the tag until all of them are set to "2" by the SPEs, and then the PPE cleans the tag to "1" to resume the SPE execution. The second method is to utilize the mailbox and signal mechanism for parallel synchronization. The PPE deploys the task to each SPE by sending signal, once receiving the "start" signal each SPE does the work from PPE. And at the time of barrier, each SPE will send "completion" event to PPE by mailbox and then sleep. Once receiving all the events from SPEs, PPE will resume the SPEs to continue to work.

## 4 Conclusion

This paper presents a parallel partition schema and three mapping model to load video processing and retrieval (VPR) workloads to Cell multi-core processor. By means of

partition and distributing the intensive computation workload to PPE and SPEs, the VPR processing is accelerated notably and a remarkable speedup is achieved. The proposed Service and Streaming models which use the mode of allocating-calling and data-streaming pipeline, are suitable and efficient, but somewhat of inconvenient. In addition, OpenMP programming model is presented on Cell to facilitate mapping VPR to Cell. Some effective strategies for data distribution and processor synchronization are also proposed by comparing the different approaches of data distribution and processor synchronization. And the overhead of the strategies for data sharing and processor synchronization are tested. The proposed partition schema and mapping model are reasonable for VPR on Cell, but there is a lot of work left to do, for example, the effectiveness of VPR mapping and the improvement of data distribution and synchronization mechanism between the PPE and the SPEs.

# Acknowledgements

We gratefully acknowledge the financial supports received from Intel Corporation for a study of multi-core programming environment

#### References

- D. Pham, S. Asano, M. Bolliger, M. N. Day, H. P. Hofstee, C. Johns, J. Kahle, A. Kameyama, J. Keaty, Y. Masubuchi, M. Riley, D. Shippy, D. Stasiak, M. Suzuoki, M. Wang, J. Warnock, S. Weitzel, D. Wendel, T. Yamazaki, and K. Yazawa: The Design and Implementation of a First-Generation CELL Processor. In: Proc. IEEE International Solid-State Circuits Conference (2005) 184-185

- IBM Microelectronics Division: PowerPC Microprocessor Family: AltiVec Technology Programming Environments Manual. IBM Corporation (2004) 282-308

- 3. Eric Li, Wenlong Li, Tao Wang, Nan Di, Carole Dulong, Yimin Zhang: Towards the Parallelization of Shot Detection a Typical Video Mining Application Study. In: Proc. 35th International Conference on Parallel Processing (2006)

- 4. IBM Corporation: IBM Full-System Simulator User's Guide version 2.0. IBM Corporation (2006)

- 5. OpenMP Architecture Review Board: OpenMP C and C++ Application Program Interface Version 2.0. http://www.openmp.org (2002)

- Feng Liu and Vipin Chaudhary: Extending OpenMP for Heterogeneous Chip Multiprocessors. In: Proc. 32nd International Conference on Parallel Processing (2003).

- Alexandre E. Eichenberger, Kathryn O'Brien, Kevin O'Brien, Peng Wu, Tong Chen, Peter H. Oden, Daniel A. Prener, Janice C. Shepherd, Byoungro So, Zehra Sura, Amy Wang, Tao Zhang, Peng Zhao, and Michael Gschwind: Optimizing Compiler for a CELL Processor. In: Proc. 14th International Conference on Parallel Architectures and Compilation Techniques (2005)

- 8. Haitao Wei, Junqing Yu: Mapping OpenMP to Cell: A Effective Compiler Framework for Heterogeneous Multi-Core Chip. In: Proc. International Workshop on OpenMP 2007 (to appear)